复旦微电子

# FM24NC512T1/T2/T3/T4 NFC Serial EEPROM

Data Sheet

Feb. 2017

INFORMATION IN THIS DOCUMENT IS INTENDED AS A REFERENCE TO ASSIST OUR CUSTOMERS IN THE SELECTION OF SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCT BEST SUITED TO THE CUSTOMER'S APPLICATION; THEY DO NOT CONVEY ANY LICENSE UNDER ANY INTELLECTUAL PROPERTY RIGHTS, OR ANY OTHER RIGHTS, BELONGING TO SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD OR A THIRD PARTY. WHEN USING THE INFORMATION CONTAINED IN THIS DOCUMENTS, PLEASE BE SURE TO EVALUATE ALL INFORMATION AS A TOTAL SYSTEM BEFORE MAKING A FINAL DECISION ON THE APPLICABILITY OF THE INFORMATION AND PRODUCTS. SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD ASSUMES NO RESPONSIBILITY FOR ANY DAMAGE, LIABILITY OR OTHER LOSS RESULTING FROM THE INFORMATION CONTAINED HEREIN. SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD PRODUCTS ARE NOT INTENDED FOR USE IN MEDICAL, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS. THE PRIOR WRITTEN APPROVAL OF SHANGHAI FUDAN MICROELECTRONICS GROUP CO., LTD IS NECESSARY TO REPRINT OR REPRODUCE IN WHOLE OR IN PART THESE DOCUMENTS.

Future routine revisions will occur when appropriate, without notice. Contact Shanghai Fudan Microelectronics Group Co., Ltd sales office to obtain the latest specifications and before placing your product order. Please also pay attention to information published by Shanghai Fudan Microelectronics Group Co., Ltd by various means, including Shanghai Fudan Microelectronics Group Co., Ltd home page (http://www.fmsh.com/).

Please contact Shanghai Fudan Microelectronics Group Co., Ltd local sales office for the specification regarding the information in this documents or Shanghai Fudan Microelectronics Group Co., Ltd products.

#### **Trademarks**

Shanghai Fudan Microelectronics Group Co., Ltd name and logo, the "复旦" logo are trademarks or registered trademarks of Shanghai Fudan Microelectronics Group Co., Ltd or its subsidiaries in China.

Shanghai Fudan Microelectronics Group Co., Ltd, Printed in the China, All Rights Reserved. 上海复旦微电子集团股份有限公司

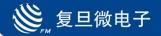

## 1 Description

FM24NC512Tx is a 512Kbit dual interface EEPROM with flexible tag function. The 512kbit data memory and the dedicated tag memory can be accessed by both two wire serial interface and ISO/IEC 14443A compatible RF interface. When tag memory accessed by RF interface, the device is fully compatible with NFC Forum Type 2 tag. The device can also access tag memory through the conventional address by two wire serial interface. This feature ensures a flexible NFC tag application.

## 2 Features

#### Contact Interface

- 1.7V~5.5V single power supply

- Typical standby current <1uA</li>

- Two wire serial interface

- 1MHz (2.5V~5.5V) and 400 kHz (1.7V~5.5V) compatibility

- Byte and Page Write (up to 128 bytes) for data memory

- Byte and Page Write (up to 16 bytes) for tag memory

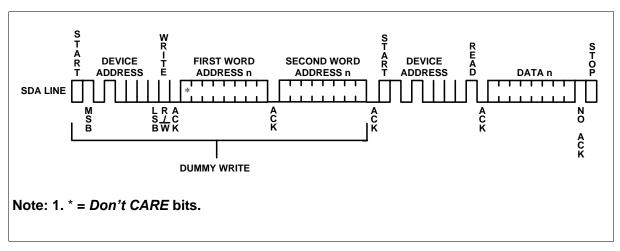

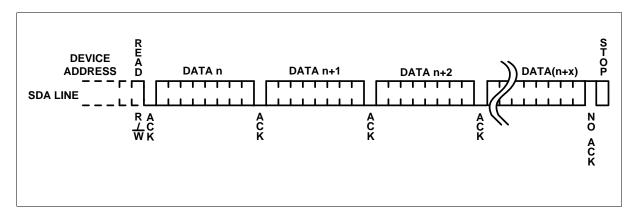

- Random and Sequential read

- Contact interface timeout

#### RF Interface

- ISO/IEC 14443A compatible

- Contactless data transmission

- Enhanced RF performance using contact power

- Carrier frequency: 13.56 MHz

- Data transfer rate: 106/212/424/848 kbit/s

- UID & Counter ASCII Mirror for automatic serialization NDEF messages

- Originality signature

- True anticollision

- Tag operation: 4 bytes Write, 16 bytes /Fast Read

- Data Memory operation: Byte and Page Write (up to 128 bytes), Random read (up to 256 bytes)

- Support sleep mode

#### Memory

- Data Memory: 64K bytes organized in 512 pages of 128 bytes each

- Tag Memory:

| Part number | Tag memory - user data |

|-------------|------------------------|

| FM24NC512T1 | 144 bytes              |

| FM24NC512T2 | 504 bytes              |

| FM24NC512T3 | 888 bytes              |

| FM24NC512T4 | 1884 bytes             |

## Self-timed write cycle (5 ms max)

- Endurance: 1 million write cycles

- Data retention: 40 years

#### Security

- Write protection register of whole data memory both in two wire serial interface and RF interface

- Write protection of tag memory by page in two wire serial interface

- Password protection for lock and system configuration and RF data write

- Unique ID for each device

### User configurable General purpose output

## Energy harvesting and Field detection

- Configurable Energy harvesting(EH) or Field detection(FD) output

- Configurable EH output voltage: 1.5V, 1.8V, 2.5V and 3.3V

- Configurable EH limited current:: 0.5mA, 1mA, 2mA and no limit

- Configurable FD output voltage: 1.5V, 1.8V, 2.5V and 3.3V

- Configurable FD trigger action: upon any RF field presence, upon the selection of the tag, upon start of frame and upon halt with previous read operation

#### Green Package

RoHS Compliant and Halogen-free

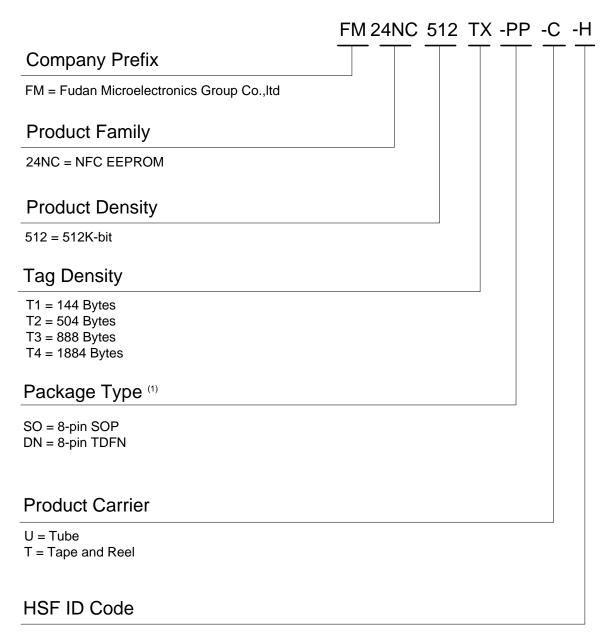

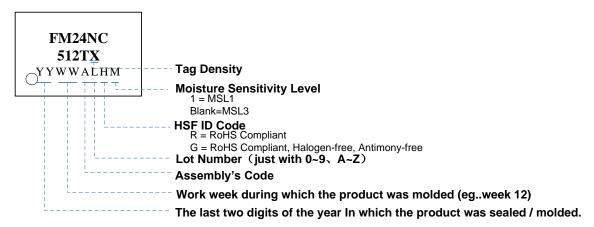

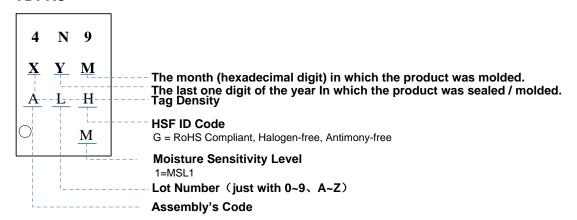

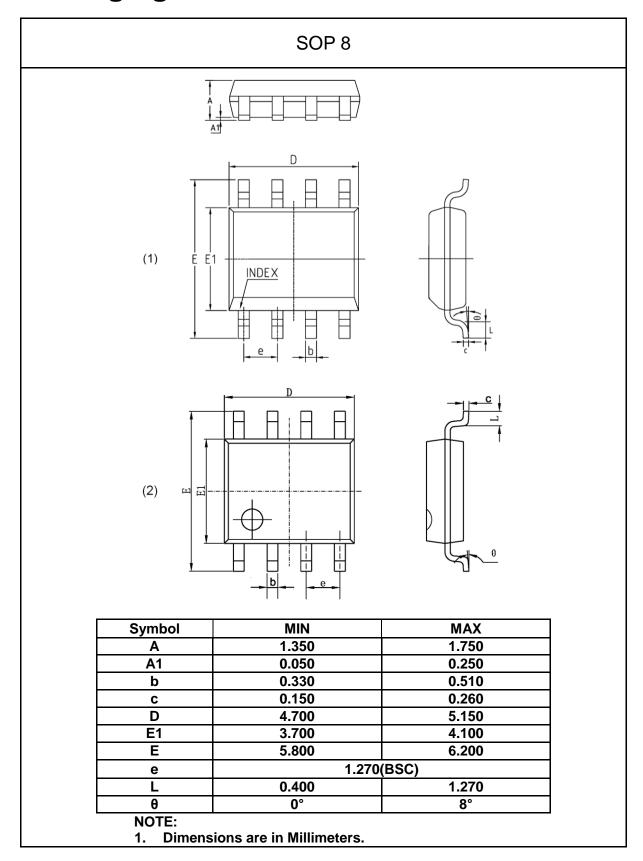

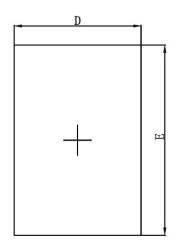

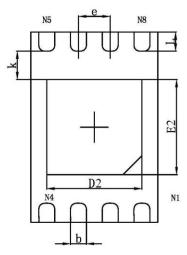

# 3 Packaging Type

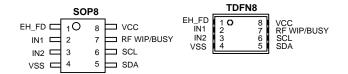

# 4 Pin Configurations

| Pin Name | Function                                     |

|----------|----------------------------------------------|

| EH_FD    | Energy harvesting and Field Detection Output |

| SDA      | Serial Data Input/Output                     |

| SCL      | Serial Clock Input                           |

| GPO      | General purpose output                       |

| IN1/IN2  | Antenna connection                           |

| VCC      | Power Supply                                 |

| VSS      | Ground                                       |

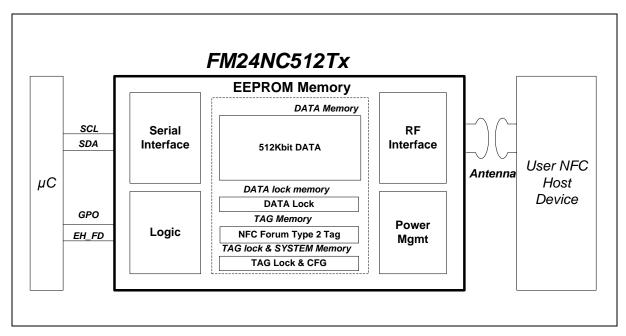

# 5 Block Diagram

Figure 1 Block Diagram of FM24NC512Tx

## 6 Pin Descriptions

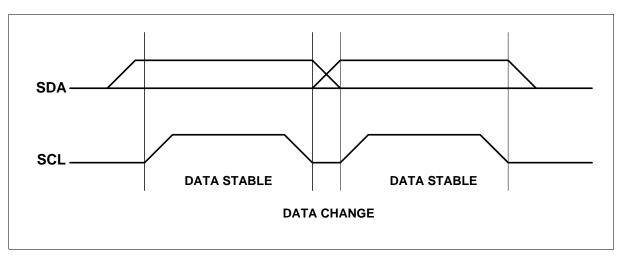

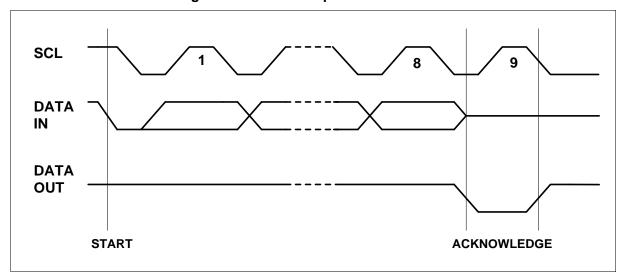

## 6.1 SERIAL CLOCK (SCL)

This input signal is used to strobe all data in and out of the device. In applications where this signal is used by slave devices to synchronize the bus to a slower clock, the bus master must have an open drain output, and a pull-up resistor must be connected from Serial Clock (SCL) to VCC. In most applications, though, this method of synchronization is not employed, and so the pull-up resistor is not necessary, provided that the bus master has a push-pull (rather than open drain) output.

## 6.2 SERIAL DATA (SDA)

This bidirectional signal is used to transfer data in or out of the device. It is an open drain output that may be wire-OR'ed with other open drain or open collector signals on the bus. A pull up resistor must be connected from Serial Data (SDA) to VCC.

## 6.3 Antenna Connection (IN1, IN2)

These input pins are used to connect the device to an external coil exclusively. It is advised to not connect any other DC or AC path to IN1 and IN2 pads. When correctly tuned, the coil is used to access the device using the ISO/IEC 14443A protocol and NFC Forum Type 2 Tag Operation Specification.

## 6.4 Energy Harvesting and Field Detection Output (EH\_FD)

This output pin is used to deliver the analog voltage available when the RF field strength is sufficient. The output voltage and the drive current can be configured.

This pin is also used as RF field detection and to interrupt source to e.g. wake up an embedded microcontroller or trigger further actions. Typical applications are Bluetooth and Wi-Fi pairing.

## 6.5 General purpose Output (GPO)

This configurable output signal is used either to indicate that the FM24NC512Tx is executing an internal write cycle of data or tag memory via RF interface or than an RF command is in progress. It is an open drain output that may be wire-OR'ed with other open drain or open collector signals on the bus. A pull up resistor must be connected from GPO to system power.

#### 6.6 Ground (VSS)

VSS is the reference for the VCC supply voltage.

## 6.7 Supply voltage (VCC)

This pin can be connected to an external DC supply voltage not only in two-wire serial interface, but also in RF interface.

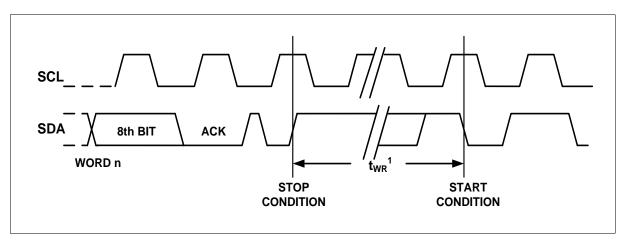

Prior to selecting the memory and issuing command to it, a valid and stable VCC voltage within the specified [VCC(min), VCC(max)] range must be applied. To maintain a stable DC supply voltage, it is recommended to decouple the VCC line with a suitable capacitor (usually of the order of 10 nF) close to the VCC/VSS package pins. This voltage must remain stable and valid until the end of the transmission of the command and, for a write command, until the completion of the internal write cycle ( $t_{WR}$ ).

# 7 Memory Organization

The FM24NC512Tx memory consists of four parts: Data memory, Data lock, Tag memory, and Tag System. Each part can be accessed by two wire serial interface or RF interface or both.

#### Table 1 Memory organization of FM24NC512Tx

#### **Data memory organization**

| Contact            | RF        | Address    |       |   | Byte number inside page |     |      |  |  |

|--------------------|-----------|------------|-------|---|-------------------------|-----|------|--|--|

| Interface          | Interface | Page       | Byte  | 0 | •••                     | 127 | on   |  |  |

| Davisa             | Data      | 000h 0000h |       |   |                         |     |      |  |  |

| Device             | Data      | 001h       | 0080h |   | Data memory             |     | Data |  |  |

| address<br>1010000 | memory    |            |       |   | (512 page X 128 byte )  |     |      |  |  |

| 1010000            | Command   | 1FFh       | FFFFh |   |                         |     |      |  |  |

#### Data system, TAG and TAG system memory organization

| Contact                      | RF                       | Add                           | ress  | E                                                                        | Byte number inside page             | 9  | Descripti |  |  |

|------------------------------|--------------------------|-------------------------------|-------|--------------------------------------------------------------------------|-------------------------------------|----|-----------|--|--|

| Interface                    | Interface                | Page                          | Byte  | 0                                                                        |                                     | 15 | on        |  |  |

| Davisa                       | NA                       | 040h                          | 0400h |                                                                          | CT_DATA_PWD & CT_DATA_WR_LOCK       |    |           |  |  |

| Device<br>address<br>1010001 | Data lock command        | 041h                          | 0410h |                                                                          | RF_DATA_WR_LOCK<br>&RF_DATA_RD_LOCK |    | Data lock |  |  |

| 1010001                      | Data pwd command         | 042h                          | 0420h |                                                                          | RF_DATA_PWD                         |    |           |  |  |

|                              |                          | 080h                          | 0800h |                                                                          | TAG memory                          |    |           |  |  |

|                              | TAG<br>memory<br>command | -   00111   001011   (   1-03 |       |                                                                          |                                     |    | TAG       |  |  |

|                              |                          |                               |       |                                                                          |                                     |    | memory    |  |  |

| Device                       |                          | 0F7h                          | 0F70h | 58 page X 16 byte for FM24NC512T3<br>120 page X 16 byte for FM24NC512T4) |                                     |    |           |  |  |

| address                      |                          | 0F8h                          | 0F80h |                                                                          | CT_TAG_WR_LOCK                      |    |           |  |  |

| 1010001                      | NA                       | 0F9h                          | 0F90h | CT_                                                                      | CT_TAG_PWD & EH_FD_CFG &<br>GPO_CFG |    |           |  |  |

|                              |                          | 0FAh                          | 0FA0h |                                                                          | UID                                 |    | & system  |  |  |

|                              |                          | OFFN OFFON NULL RF            |       |                                                                          | RF_S<br>LEEP                        | -  |           |  |  |

**Remark**: The address not mentioned is NULL, which indicates the empty address. When accessed by contact interface, the readout data is always 00h. The write operation in this area receives the response of ACK and will trigger internal write cycle, but it cannot change the readout data.

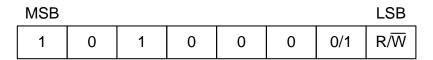

## 7.1 Data memory

The data memory of FM24NC512Tx is organized in 512 pages of 128 bytes each. When accessed by two wire serial interface, with device address set to 1010000b, each byte can be individually read or write using 2 bytes of byte address which address range is from 0000h to FFFFh. When accessed by RF interface, with data memory command, each byte can be individually read or write using 2 bytes of byte address which address range is from 0000h to FFFFh.

There is a special mechanism to protect data memory from unexpected write operation. For command from two wire serial interface, the whole data memory is protected by the CT\_DATA\_WR\_LOCK register. The write operation is permitted if only the register=0. For command from RF interface, the whole data memory is protected by the RF\_DATA\_WR\_LOCK register and RF\_DATA\_PWD authentication action. The write operation is permitted if only the

register=0 and a previously RF\_DATA\_PWD authentication.

The default value of the data memory at delivery is FFh.

## 7.2 Data lock memory

### 7.2.1 CT\_DATA\_WR\_LOCK(0400h)

CT\_DATA\_WR\_LOCK is a register that locks the write access of data memory in contact interface.

The detail is shown as below

#### CT\_DATA\_WR\_LOCK register

| Byte addr. | Bit number inside byte  |   |   |   |     |   |   |   |  |  |

|------------|-------------------------|---|---|---|-----|---|---|---|--|--|

| addr.      | 7                       | 6 | 5 | 4 | 3   | 2 | 1 | 0 |  |  |

| 0400h      | CT_DAT<br>A_WR_L<br>OCK |   |   |   | RFU |   |   |   |  |  |

- 0b indicates to unlock data memory

- 1b indicates to lock data memory

In contact interface, the read access of CT\_DATA\_WR\_LOCK doesn't need authentication of contact password (CT\_DATA\_PWD). However, the write access must be in CT\_DATA\_PWD authenticated state.

CT\_DATA\_WR\_LOCK does not impact write access of RF interface, and it couldn't be accessed in RF interface.

The default value of each bit of CT\_DATA\_WR\_LOCK at delivery is 0b.

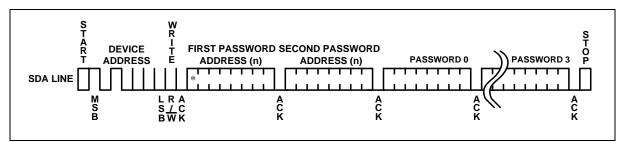

### 7.2.2 CT\_DATA\_PWD(0408h~040Bh)

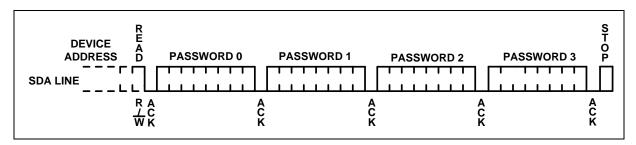

CT\_DATA\_PWD is password of contact interface. It has 32 bits organized in 4 bytes, which byte address is from 0408h to 040Bh in contact interface. CT\_PWD is used to password authentication in contact interface.

CT\_DATA\_PWD can be read and write in password authenticated state of contact interface.

CT\_DATA\_PWD cannot be accessed by RF interface.

The default value of each byte of CT\_PWD at delivery is 00h.

## 7.2.3 RF\_DATA\_WR\_LOCK(0418h)

RF\_DATA\_WR\_LOCK is a register that locks the write access of data memory in RF interface. The detail is shown as below

#### CT DATA WR LOCK register

| Byte  | Bit number inside byte  |   |   |   |     |   |   |   |  |  |

|-------|-------------------------|---|---|---|-----|---|---|---|--|--|

| addr. | 7                       | 6 | 5 | 4 | 3   | 2 | 1 | 0 |  |  |

| 0418h | RF_DAT<br>A_WR_L<br>OCK |   | - | _ | RFU |   | - | _ |  |  |

- 0b indicates to unlock data memory

- 1b indicates to lock data memory

上海复旦微电子集团股份有限公司

In RF interface, the read access of RF\_DATA\_WR\_LOCK doesn't need authentication of RF password (RF\_DATA\_PWD). However, the write access must be in RF\_DATA\_PWD authenticated state.

RF\_DATA\_WR\_LOCK does not impact write access of contact interface.

The default value of each bit of RF\_DATA\_WR\_LOCK at delivery is 0b.

### 7.2.4 RF\_DATA\_RD\_LOCK(0410h)

RF\_DATA\_RD\_LOCK is a register that locks the read access of data memory in RF interface.

The detail is shown as below

## CT\_DATA\_WR\_LOCK register

| Byte  | Bit number inside byte  |   |   |   |     |   |   |   |  |  |

|-------|-------------------------|---|---|---|-----|---|---|---|--|--|

| addr. | 7                       | 6 | 5 | 4 | 3   | 2 | 1 | 0 |  |  |

| 0410h | RF_DAT<br>A_RD_L<br>OCK |   |   |   | RFU |   |   |   |  |  |

- 0b indicates to unlock data memory

- 1b indicates to lock data memory

In RF interface, the read access of RF\_DATA\_WR\_LOCK doesn't need authentication of RF password (RF\_DATA\_PWD). However, the write access must be in RF\_DATA\_PWD authenticated state.

RF\_DATA\_RD\_LOCK does not impact read access of contact interface.

The default value of each bit of RF\_DATA\_RD\_LOCK at delivery is 0b.

## 7.2.5 RF\_DATA\_PWD(0420h~0423h)

RF\_DATA\_PWD is password of RF interface. It has 32 bits organized in 4 bytes, which byte address is from 0420h to 0423h in contact interface. RF\_PWD is used to password authentication in RF interface.

RF DATA PWD can be read and write in password authenticated state of contact interface.

RF\_DATA\_PWD can not be accessed by RF interface.

The default value of each byte of RF\_DATA\_PWD at delivery is 00h.

## 7.3 Tag memory

In FM24NC512Tx, there's a tag memory to ensure NFC Forum Type 2 Tag operation. It can be accessed by two wire serial interface, with device address set to 1010001b, using 2 bytes of byte address. The address range varies according to tag type, refers to Table 2-5.

The tag memory is organized in pages of 16 bytes each when accessed by two wire serial interface. Meanwhile, the tag memory is organized in blocks of 4 bytes each when accessed by RF interface. Each block can be individually accessed by tag command.

For FM24NC512T1 variant, the tag memory size is 180 bytes, including 144 bytes user memory. NFC Tag is organized in blocks with 4 bytes. Each block can be individually accessed by tag command.

Table 2 Tag memory organization of FM24NC512T1

|--|

上海复旦微电子集团股份有限公司

| Device                | 3 -       |       |      | ock<br>dr. | 0                         | 1                                                   | 2                | 3                |                       |  |  |

|-----------------------|-----------|-------|------|------------|---------------------------|-----------------------------------------------------|------------------|------------------|-----------------------|--|--|

| addr                  | addr.     | addr. | Hex. | Dec.       |                           |                                                     | _                |                  |                       |  |  |

|                       |           | 0800h | 00h  | 0          | UID0/RFU                  | UID1/RFU                                            | UID2/RFU         | BCC0/RFU         | UID and               |  |  |

|                       |           | 0804h | 01h  | 1          | UID3/RFU                  | UID4/RFU                                            | UID5/RFU         | UID6/RFU         | static lock           |  |  |

|                       | 080h      | 0808h | 02h  | 2          | BCC1/RFU                  | Internal/RF<br>U                                    | Lock_byte[<br>0] | Lock_byte[<br>1] | bytes                 |  |  |

|                       | ~<br>083h | 080Ch | 03h  | 3          | Capability C              | Container (CO                                       | C)               |                  | CC                    |  |  |

|                       | UOSII     | 0810h | 04h  | 4          | 04-4'- D-4-               |                                                     |                  |                  |                       |  |  |

|                       |           |       |      |            | - 10111 - 01101           | Static Data Area<br>Block 04h-0Fh, total 12 blocks) |                  |                  |                       |  |  |

|                       |           | 083Ch | 0Fh  | 15         | (DIOCK 04II-              | User data                                           |                  |                  |                       |  |  |

| 101000                |           | 0840h | 10h  | 16         | D D                       | User data                                           |                  |                  |                       |  |  |

| 1                     |           |       |      |            | Dynamic Da<br>(Block 10h~ |                                                     |                  |                  |                       |  |  |

|                       |           | 089Ch | 27h  | 39         | (DIOCK TOTI~              | 2DII, IOIAI 2-                                      | + DIOCKS)        |                  |                       |  |  |

|                       | 084h      | 08A0h | 28h  | 40         | Dynamic Lo                | ck Bytes                                            |                  |                  | Dynamic<br>Lock Bytes |  |  |

|                       | ~<br>08Bh | 08A4h | 29h  | 41         | FDP & MIRROR              | RFU                                                 | MIRROR_<br>BLOCK | AUTH0            |                       |  |  |

|                       |           | 08A8h | 2Ah  | 42         | ACCESS                    | RFU                                                 |                  |                  | Configuratio          |  |  |

|                       |           | 08ACh | 2Bh  | 43         | PWD                       |                                                     |                  |                  | n                     |  |  |

| 08B0h 2Ch 44 PACK RFU |           |       |      |            |                           |                                                     |                  |                  |                       |  |  |

| ;                     | See 7.4   | 1     | 2Dh  | 45         | EH_FD_C<br>FG             | GPO_CFG                                             | RFU              |                  | Tag system            |  |  |

For FM24NC512T2, the tag memory size is 540 bytes, including 504 bytes user memory. NFC Tag is organized in blocks with 4 bytes. Each block can be individually accessed by tag command.

Table 3 Tag memory organization of FM24NC512T2

| Cor    | ntact Cl                         | MD    | Tag                      | CMD  | В                       | yte number                                          |                       |                  |                      |  |

|--------|----------------------------------|-------|--------------------------|------|-------------------------|-----------------------------------------------------|-----------------------|------------------|----------------------|--|

| Device | Device Page Byte addr addr. addr |       | Block addr.              |      | 0                       | 1                                                   | 2                     | 3                | Description          |  |

| udui   | addi.                            | uuui. | Hex.                     | Dec. |                         |                                                     |                       |                  |                      |  |

|        |                                  | 0800h | 00h                      | 0    | UID0/RFU                | UID1/RFU                                            | UID2/RFU              | BCC0/RFU         | UID and              |  |

|        |                                  | 0804h | 01h                      | 1    | UID3/RFU                |                                                     |                       |                  |                      |  |

|        | 080h                             | 0808h | 02h                      | 2    | BCC1/RFU                | Internal/RF<br>U                                    | Lock_byte[<br>0]      | Lock_byte[<br>1] | static lock<br>bytes |  |

|        | ~<br>083h                        | 080Ch | 03h                      | 3    | (                       | Capability Container (CC)                           |                       |                  |                      |  |

|        | 00311                            | 0810h | 04h                      | 4    |                         | Static Data Area                                    |                       |                  |                      |  |

|        |                                  |       |                          |      | (Blo                    | (Block 04h-0Fh, total 12 blocks)                    |                       |                  |                      |  |

| 101000 |                                  | 083Ch | 0Fh                      | 15   | (Did                    | User data                                           |                       |                  |                      |  |

| 1      |                                  | 0840h | 10h                      | 16   |                         | D D                                                 |                       |                  |                      |  |

| -      |                                  |       |                          |      | (Bloc                   | Dynamic Data Area (Block 10h~81h, total 114 blocks) |                       |                  |                      |  |

|        |                                  | 0A04h | 81h                      | 129  | (Diot                   | JK TOH~OTH,                                         | total 114 bic         | ocks)            |                      |  |

|        | 084h<br>~                        |       |                          |      |                         |                                                     | Dynamic<br>Lock Bytes |                  |                      |  |

|        | 0A1h                             | 0A0Ch | 83h                      | 131  | FDP & RFU MIRROR_ AUTHO |                                                     |                       |                  | Configuratio         |  |

|        |                                  | 0A10h | DA10h 84h 132 ACCESS RFU |      |                         |                                                     |                       | n                |                      |  |

|        |                                  | 0A14h | 85h                      | 133  |                         | PV                                                  | VD                    |                  |                      |  |

| Cor            | ntact Cl   | MD    | Tag         | CMD  | В                     | k    |                       |                |    |    |             |

|----------------|------------|-------|-------------|------|-----------------------|------|-----------------------|----------------|----|----|-------------|

| Device<br>addr | Page addr. | Byte  | Block addr. |      |                       |      | 0                     | 1              | 2  | 3  | Description |

| addr           | addr.      | addr. | Hex.        | Dec. |                       |      |                       |                |    |    |             |

|                |            | 0A18h | 86h         | 134  | PA                    | PACK |                       | <del>-</del> U |    |    |             |

|                | See 7.4    |       | .4 87h 135  |      | EH_FD_C<br>FG GPO_CFG |      | EH_FD_C<br>FG GPO_CFG |                | RI | -U | Tag system  |

For FM24NC512T3, the tag memory size is 924 bytes, including 888 bytes user memory. NFC Tag is organized in blocks with 4 bytes. Each block can be individually accessed by tag command.

Table 4 Tag memory organization of FM24NC512T3

| Coi            | ntact C       | MD         | Tag | CMD                | В               | yte number       | inside bloc      | k                |                       |  |

|----------------|---------------|------------|-----|--------------------|-----------------|------------------|------------------|------------------|-----------------------|--|

| Device<br>addr | Page<br>addr. | Byte addr. |     | ock<br>dr.<br>Dec. | 0               | 1                | 2                | 3                | Description           |  |

|                |               | 0800h      | 00h | 0                  | UID0/RFU        | UID1/RFU         | UID2/RFU         | BCC0/RFU         |                       |  |

|                |               | 0804h      | 01h | 1                  | UID3/RFU        | UID4/RFU         | UID5/RFU         | UID6/RFU         | UID and static lock   |  |

|                | 080h          | 0808h      | 02h | 2                  | BCC1/RFU        | Internal/RF<br>U | Lock_byte[<br>0] | Lock_byte[<br>1] | bytes                 |  |

|                | ~<br>000b     | 080Ch      | 03h | 3                  | Capability C    | Container (Co    | C)               | _                | CC                    |  |

|                | 083h          | 0810h      | 04h | 4                  | 0 5 .           |                  |                  |                  |                       |  |

|                |               |            |     |                    | Static Data     | 1                |                  |                  |                       |  |

|                |               | 083Ch      | 0Fh | 15                 | (Block 04h-     |                  |                  |                  |                       |  |

| 101000         |               | 0840h      | 10h | 16                 |                 | User data        |                  |                  |                       |  |

| 1              |               |            |     |                    | Dynamic Da      |                  |                  |                  |                       |  |

|                |               | 0B84h      | E1h | 225                | (DIOCK TOTI~    | E1h, total 2     | TO DIOCKS)       |                  |                       |  |

|                | 084h          | 0B88h      | E2h | 226                | Dynamic Lo      | ck Bytes         |                  |                  | Dynamic<br>Lock Bytes |  |

|                | ~<br>0B9h     | 0B8Ch      | E3h | 227                | FDP &<br>MIRROR | RFU              | MIRROR_<br>BLOCK | AUTH0            |                       |  |

|                |               | 0B90h      | E4h | 228                | ACCESS          | RFU              |                  |                  | Configuratio          |  |

|                |               | 0B94h      | E5h | 229                | PWD             |                  |                  |                  | n                     |  |

|                |               | 0B98h      | E6h | 230                | PACK            |                  | RFU              |                  |                       |  |

| ;              | See 7.4 E7    |            |     |                    | EH_FD_C<br>FG   | GPO_CFG          | RFU              |                  | Tag system            |  |

For FM24NC512T4, the tag memory size is 1920 bytes, including 1884 bytes user memory. NFC Tag is organized in blocks with 4 bytes. Each block can be individually accessed by tag command.

Table 5 Tag memory organization of FM24NC512T4

| Con    | tact C       | MD     | Tag          | g CMD | )          | Byt     | te number | inside bl | ock     |         |       |

|--------|--------------|--------|--------------|-------|------------|---------|-----------|-----------|---------|---------|-------|

| Device | Page<br>addr | Byte   | Sector addr. |       | ock<br>dr. | 0       | 1         | 2         | 3       | Descrip | otion |

| addr   |              | addr.  |              | Hex.  | Dec.       |         |           |           |         |         |       |

| 101000 | 080h         | 0800h  | 0            | 00h   | 0          | UID0/RF | UID1/RF   | UID2/RF   | BCC0/RF | UID     | and   |

| 1      | ~            | UOUUII | U            | UUII  | U          | U       | U         | U         | U       | static  | lock  |

| Con     | tact C    | MD         | Ta     | g CME |      | Byt          | te numbe               | r inside bl      | ock              |                       |

|---------|-----------|------------|--------|-------|------|--------------|------------------------|------------------|------------------|-----------------------|

| Device  | Page      | Dista      | Sector | Blo   | ock  |              |                        |                  |                  | Description           |

| addr    | addr      | Byte addr. | addr.  | ad    | dr.  | 0            | 1                      | 2                | 3                | Description           |

| auui    |           | auui.      |        | Hex.  | Dec. |              |                        |                  |                  |                       |

|         | 083h      | 0804h      |        | 01h   | 1    | U            | UID4/RF<br>U           | U                | U                | bytes                 |

|         |           | 0808h      |        | 02h   | 2    | BCC1/RF<br>U | Internal/<br>RFU       | Lock_byt e[0]    | Lock_byt<br>e[1] |                       |

|         |           | 080Ch      |        | 03h   | 3    | Capability   | Containe               | r (CC)           |                  | CC                    |

|         |           | 0810h      |        | 04h   | 4    | 01.11.10.11  |                        |                  |                  |                       |

|         |           |            |        |       |      | Static Dat   |                        | al 12 blocks     | -1               |                       |

|         |           | 083Ch      |        | 0Fh   | 15   | (DIOCK U41   | ו-טרוו, וטומ           | al IZ DIOCK      | >)               |                       |

|         |           | 0840h      |        | 10h   | 16   |              |                        |                  |                  |                       |

|         |           |            |        |       |      |              |                        |                  |                  | User data             |

|         |           | 0BFC<br>h  |        | FFh   | 255  | -            | Data Area<br>) Block 1 | 0h~Sector        | · 1 Block        |                       |

|         |           | 0C00h      |        | 00h   | 0    | DAh, total   | 459 Block              | ks)              |                  |                       |

|         |           |            |        |       |      |              |                        |                  |                  |                       |

|         | 084h      | 0F68h      |        | DAh   | 218  |              |                        |                  |                  |                       |

|         | ~<br>0F7h | 0F6Ch      |        | DBh   | 219  | Dynamic I    | Lock Bytes             | 5                |                  | Dynamic<br>Lock Bytes |

|         |           | 0F70h      | 1      | DCh   | 220  | FDP & MIRROR | RFU                    | MIRROR<br>_BLOCK | AUTH0            |                       |

|         |           | 0F74h      |        | DDh   | 221  | ACCESS       | RFU                    |                  | SEC_CF<br>G      | Configuratio n        |

|         |           | 0F78h      |        | DEh   | 222  | PWD          |                        |                  |                  |                       |

|         |           | 0F7Ch      |        | DFh   | 223  | PACK         |                        | RFU              |                  |                       |

| See 7.4 |           |            |        | E0h   | 224  |              | GPO_CF<br>G            | RFU              |                  | Tag system            |

#### 7.3.1 Read only bytes(0800h~0809h)

In RF interface, these 10 bytes are the mirror of UID, which are read only. Any read operation replies UID which defined in UID (0FA0h~0FA9h). In contact interface, these 10 bytes can be written to any data, and be readout. But it can not change the reply of read operation of RF interface.

**Remark**: The real UID and anticollision operation will not be influenced if these bytes are changed by contact interface.

### 7.3.2 Static lock bytes(080Ah~080Bh)

In RF interface, the bits of byte 2 and byte 3 of block 02h represent the field programmable read-only locking mechanism. Each block from 03h (CC) to 0Fh can be individually locked by setting the corresponding locking bit Lx to logic 1 to prevent further write access. After locking, the corresponding block becomes read-only memory.

The three least significant bits of lock byte 0 are the block-locking bits. Bit 2 deals with block 0Ah to 0Fh, bit 1 deals with block 04h to 09h and bit 0 deals with block 03h (CC). Once the block-locking bits are set Logic 1, the locking configuration for the corresponding memory area is frozen.

Table 6 Static lock bytes of FM24NC512Tx

| Field | Byte | Bit number inside byte |

|-------|------|------------------------|

|       |      |                        |

## Shanghai Fudan Microelectronics Group Company Limited

|    | 复旦微电 | 子 |

|----|------|---|

| EM |      |   |

|                   | No. | 7   | 6   | 5   | 4   | 3   | 2       | 1     | 0    |

|-------------------|-----|-----|-----|-----|-----|-----|---------|-------|------|

| Static lock bytes | 0   | L7  | L6  | L5  | L4  | LCC | BL15-10 | BL9-4 | BLCC |

| Static lock bytes | 1   | L15 | L14 | L13 | L12 | L11 | L10     | L9    | L8   |

**Remark**: Lx locks Block x to read-only; BLx-y blocks further locking for the memory area x-y.

For example if BL15-10 is set to logic 1, then bits L15 to L10 (lock byte 1, bit [7:2]) can no longer be changed.

The so called static locking and block-locking bits are set by a WRITE or COMPATIBILITY\_WRITE command to block 02h. Bytes 2 and 3 of the WRITE or COMPATIBILITY\_WRITE command and the contents of the lock bytes are bit-wise OR'ed and the result then becomes the new content of the lock bytes. This process is irreversible. If a bit is set to logic 1, it cannot be changed back to logic 0. The contents of bytes 0 and 1 of block 02h are unaffected by the corresponding data bytes of the WRITE or COMPATIBILITY WRITE command.

In contact interface, static lock bytes don't affect the write access of tag memory.

The default value of the static lock bytes at delivery is 00h.

## 7.3.3 Dynamic Lock Bytes

In RF interface, to lock the blocks starting at block address 10h and onwards, the so called dynamic lock bytes are used.

For FM24NC512T1 variant, those three lock bytes cover the memory area of 96 data bytes. The granularity is 2 blocks, compared to a single block for the first 64 bytes as shown in Table 7.

For FM24NC512T2 variant, those four lock bytes cover the memory area of 456 data bytes. The granularity is 16 blocks, compared to a single block for the first 64 bytes as shown in Table 8.

For FM24NC512T3 variant, those four lock bytes cover the memory area of 840 data bytes. The granularity is 16 blocks, compared to a single block for the first 64 bytes as shown in Table 9.

For FM24NC512T4 variant, those four lock bytes cover the memory area of 1884 data bytes. The granularity is 16 blocks, compared to a single block for the first 64 bytes as shown in Table 10.

Remark: Set all bits marked with RFU to 0, when writing to the dynamic lock bytes.

Table 7 Dynamic Lock Byte of FM24NC512T1

| Field  | Byte |        |        | В       | it number | inside by | rte     |         |         |

|--------|------|--------|--------|---------|-----------|-----------|---------|---------|---------|

| rieid  | No.  | 7      | 6      | 5       | 4         | 3         | 2       | 1       | 0       |

| Dynami | 0    | L30-31 | L28-29 | L26-27  | L24-25    | L22-23    | L20-21  | L18-19  | L16-17  |

| C      | 1    | RFU    | RFU    | RFU     | RFU       | L38-39    | L36-37  | L34-35  | L32-33  |

| lock   | 2    | RFU    | RFU    | BL36-39 | BL32-25   | BL28-31   | BL24-27 | BL20-23 | BL16-19 |

| byte   | 3    | RFU    | •      |         | •         | •         | ,       | •       |         |

Remark: Lx-y locks Block x-y to read-only; BLx-y blocks further locking for Block x-y.

Table 8 Dynamic Lock Byte of FM24NC512T2

| Field           | Byte |          |          |         | Bit numbe | r inside byte | )        |         |         |

|-----------------|------|----------|----------|---------|-----------|---------------|----------|---------|---------|

| rieiu           | No.  | 7        | 6        | 5       | 4         | 3             | 2        | 1       | 0       |

|                 | 0    | L128-129 | L112-127 | L96-111 | L80-95    | L64-79        | L48-63   | L32-47  | L16-31  |

| Dynamic<br>lock | 1    | RFU      |          |         |           |               |          |         |         |

| byte            | 2    | RFU      |          |         |           | BL112-129     | BL80-111 | BL48-79 | BL16-47 |

|                 | 3    | RFU      |          |         |           | •             |          |         |         |

**Remark**: Lx-y locks Block x-y to read-only. BLx-y blocks further locking for Block x-y.

Table 9 Dynamic Lock Byte of FM24NC512T3

| Field        | Byte |          | Bit number inside byte |           |               |               |          |          |          |  |  |  |  |

|--------------|------|----------|------------------------|-----------|---------------|---------------|----------|----------|----------|--|--|--|--|

| rieia        | No.  | 7        | 6                      | 5         | 4             | 3             | 2        | 1        | 0        |  |  |  |  |

|              | 0    | L128-143 | L112-127               | L96-111   | L80-95        | L64-79        | L48-63   | L32-47   | L16-31   |  |  |  |  |

| Dynamic      | 1    | RFU      |                        | _         | L208-223      | -             | L176-191 | L160-175 | L144-159 |  |  |  |  |

| lock<br>byte | 2    | RFU      | BL208-225              | BL176-207 | BL144-17<br>5 | BL112-14<br>3 | BL80-111 | BL48-79  | BL16-47  |  |  |  |  |

|              | 3    | RFU      |                        |           |               |               |          |          |          |  |  |  |  |

**Remark**: Lx-y locks Block x-y to read-only; BLx-y blocks further locking for Block x-y.

Table 10 Dynamic Lock Byte of FM24NC512T4

| Field        | Byte | Bit number inside byte |           |           |               |               |               |          |          |  |  |  |

|--------------|------|------------------------|-----------|-----------|---------------|---------------|---------------|----------|----------|--|--|--|

| rieid        | No.  | 7                      | 6         | 5         | 4             | 3             | 2             | 1        | 0        |  |  |  |

|              | 0    | L240-271               | L208-239  | L176-207  | L144-175      | L112-143      | L80-111       | L48-79   | L16-47   |  |  |  |

| Dynamic      | 1    | RFU                    | L464-474  | L432-463  | L400-431      | L368-399      | L336-367      | L304-335 | L272-303 |  |  |  |

| lock<br>byte | 2    | BL464-474              | BL400-463 | BL336-399 | BL272-33<br>5 | BL208-27<br>1 | BL144-20<br>7 | BL80-143 | BL16-79  |  |  |  |

|              | 3    | RFU                    |           |           |               |               |               |          |          |  |  |  |

**Remark**: Lx-y locks Block x-y to read-only; BLx-y blocks further locking for Block x-y. There are 459 dynamic data blocks, 240 blocks in sector 0 and 219 blocks in sector 1, respectively.

Dynamic lock bytes of the WRITE or COMPATIBILITY\_WRITE command and the current contents of the dynamic lock bytes is bit-wise OR'ed. The result is the new dynamic lock bytes contents. This process is irreversible. Once a bit is set to logic 1, it cannot be changed back to logic 0.

In contact interface, dynamic lock bytes don't affect the write access of tag memory.

The default value of dynamic lock bytes at delivery is 00h.

## 7.3.4 Capability Container (CC) bytes(080Ch~080Fh)

The Capability Container CC (block 3) is programmed during the IC production according to the NFC Forum Type 2 Tag specification. These bytes may be bit-wise modified by a WRITE or COMPATIBILITY\_WRITE command.

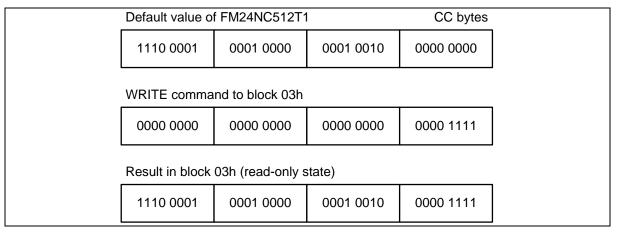

Figure 2 the example of CC bytes write

The parameter bytes of the WRITE command and the current contents of the CC bytes are bit-wise OR'ed. The result is the new CC byte contents. This process is irreversible. Once a bit is set to logic 1, it cannot be changed back to logic 0.

The default values of the CC bytes at delivery are defined in Section 7.3.6.

#### 7.3.5 Data blocks

Blocks 04h to 27h for FM24NC512T1, blocks 04h to 81h for FM24NC512T2, blocks 04h to E1h for FM24NC512T3 and blocks 04h of sector 0 to DAh of sector 1 for FM24NC512T4 are the user memory read/write area. The access to a part of the user memory area can be restricted using password verification. See Section 7.3.7 for further details.

The default values of the data blocks at delivery are defined in Section 7.3.6.

## 7.3.6 CC and Data blocks content at delivery

The tag memory of FM24NC512Tx are pre-programmed to the initialized state according to the NFC Forum Type 2 Tag specification as defined in Table 11, Table 12, Table 13 and Table 14.

Table 11 Memory content at delivery of FM24NC512T1

| Conta      | ct CMD     | Tag CMD Byte number inside block |     |     | block |     |

|------------|------------|----------------------------------|-----|-----|-------|-----|

| Page addr. | Byte addr. | Block addr.                      | 0   | 1   | 2     | 3   |

|            | 080Ch      | 03h                              | E1h | 10h | 12h   | 00h |

| 0006       | 0810h      | 04h                              | 01h | 03h | A0h   | 0Ch |

| 080h       | 0814h      | 05h                              | 34h | 03h | 03h   | D0h |

|            | 0818h      | 06h                              | 00h | 00h | FEh   | 00h |

Table 12 Memory content at delivery of FM24NC512T2

| Conta      | ct CMD     | Tag CMD     | E   | Byte number inside block |     |     |  |  |

|------------|------------|-------------|-----|--------------------------|-----|-----|--|--|

| Page addr. | Byte addr. | Block addr. | 0   | 1                        | 2   | 3   |  |  |

|            | 080Ch      | 03h         | E1h | 10h                      | 3Fh | 00h |  |  |

| 0006       | 0810h      | 04h         | 01h | 03h                      | 88h | 08h |  |  |

| 080h       | 0814h      | 05h         | 66h | 03h                      | 03h | D0h |  |  |

|            | 0818h      | 06h         | 00h | 00h                      | FEh | 00h |  |  |

Table 13 Memory content at delivery of FM24NC512T3

| Conta      | ct CMD     | Tag CMD     | E   | Byte number inside block |     |     |  |  |  |

|------------|------------|-------------|-----|--------------------------|-----|-----|--|--|--|

| Page addr. | Byte addr. | Block addr. | 0   | 1                        | 2   | 3   |  |  |  |

|            | 080Ch      | 03h         | E1h | 10h                      | 6Fh | 00h |  |  |  |

| 0006       | 0810h      | 04h         | 01h | 03h                      | E8h | 0Eh |  |  |  |

| 080h       | 0814h      | 05h         | 66h | 03h                      | 03h | D0h |  |  |  |

|            | 0818h      | 06h         | 00h | 00h                      | FEh | 00h |  |  |  |

Table 14 Memory content at delivery of FM24NC512T4

| Contact CMD |            | Tag CMD     | В   | Byte number inside block |     |     |  |  |  |

|-------------|------------|-------------|-----|--------------------------|-----|-----|--|--|--|

| Page addr.  | Byte addr. | Block addr. | 0   | 1                        | 2   | 3   |  |  |  |

|             | 080Ch      | 03h         | E1h | 10h                      | 6Fh | 00h |  |  |  |

| 080h        | 0810h      | 04h         | 01h | 03h                      | E8h | 0Eh |  |  |  |

|             | 0814h      | 05h         | 66h | 03h                      | 03h | D0h |  |  |  |

| Contac     | ct CMD     | Tag CMD     | te numbe | umber inside block |     |     |

|------------|------------|-------------|----------|--------------------|-----|-----|

| Page addr. | Byte addr. | Block addr. | 0        | 1                  | 2   | 3   |

|            | 0818h      | 06h         | 00h      | 00h                | FEh | 00h |

The access to a part of the user memory area of tag memory can be restricted using password verification. Please see Section 7 for further details.

#### 7.3.7 Configuration

Blocks 29h to 2Ah for FM24NC512T1 variant, blocks 83h to 84h for FM24NC512T2 variant, blocks E3h to E4h for FM24NC512T3 variant and blocks DCh to DDh of sector 1 variant are used to configure the memory access restriction and to configure the UID ASCII mirror feature.

Blocks 2Bh to 2Ch for FM24NC512T1 variant, blocks 85h to 86h for FM24NC512T2 variant, blocks E5h to E6h for FM24NC512T3 variant and blocks DEh to DFh of sector 1 variant are used as password and PACK.

Table 15 MIRROR\_BYTE configuration

| Byte                                | Block                                    | Field           |              | Bit number inside byte |            |       |              |                 |                 |     |  |  |  |  |

|-------------------------------------|------------------------------------------|-----------------|--------------|------------------------|------------|-------|--------------|-----------------|-----------------|-----|--|--|--|--|

| address                             | address                                  | rieiu           | 7            | 6                      | 5          | 4     | 3            | 2               | 1               | 0   |  |  |  |  |

| 08A4h/<br>0A0Ch/<br>0B8Ch/<br>0F70h | 29h/<br>83h/<br>E3h/<br>DCh<br>(Sector1) | FDP &<br>MIRROR | MIRROI<br>NF | R_CO                   | MIRRC<br>E | R_BYT | SLEEP_E<br>N | STRG_M<br>OD_EN | FDP <sub></sub> | _CO |  |  |  |  |

**Remark**: Byte/Block address is for FM24NC512T1, FM24NC512T2, FM24NC512T3 and FM24NC512T4 individually.

**Table 16 ACCESS configuration**

| Duta address | Block   | Field  | Bit number inside byte |       |   |       |       |         |     |      |  |  |

|--------------|---------|--------|------------------------|-------|---|-------|-------|---------|-----|------|--|--|

| Byte address | address | rieiu  | 7                      | 6     | 5 | 4     | 3     | 2       | 1   | 0    |  |  |

| 08A8h        | 2Ah     |        |                        |       |   |       | NFC_C |         |     |      |  |  |

| 0A10h        | 84h     | ۸۵۵۲۵۵ | PROT                   | CFGLC |   | NFC_C | NT_PW | A 1 17  |     | 18.4 |  |  |

| 0B90h        | E4h     | ACCESS |                        | K     |   | NT_EN | D_PRO | AUTHLIM | IVI |      |  |  |

| 0F74h        | DDh     |        |                        |       |   |       | T_EN  |         |     |      |  |  |

**Remark**: Byte/Block address is for FM24NC512T1, FM24NC512T2, FM24NC512T3 and FM24NC512T4 individually.

Table 17 SEC\_CFG configuration

| Byte address | Block   | Field  | Bit number inside byte |   |   |   |             |       |   |   |  |  |

|--------------|---------|--------|------------------------|---|---|---|-------------|-------|---|---|--|--|

| byte address | address | rieiu  | 7                      | 6 | 5 | 4 | 3           | 2     | 1 | 0 |  |  |

| 0F77h        | DDh     | ACCESS | RFU                    |   |   |   | MIRRO<br>RS | AUTHS |   |   |  |  |

**Remark**: Byte/Block address is for FM24NC512T4, this configuration makes sense only for FM24NC512T4.

**Table 18 TAG configuration parameter description**

| Part number | Byte address | Block address | Field            | Bit | Default values | description                                                                                                                                                                                                                                                                                                                                                |

|-------------|--------------|---------------|------------------|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FM24NC512T1 |              | 29h           | MIRROR_CON<br>F  | 2   | 00b            | Defines which ASCII mirror shall be used, if the ASCII mirror is enabled by a valid MIRROR_BLOCK byte 00b no ASCII mirror 01b UID ASCII mirror 10b Counter mirror 11b UID & counter mirror                                                                                                                                                                 |

| FM24NC512T1 | 08A4h        | 29h           | MIRROR_BYT<br>E  | 2   | 00b            | The 2 bits define the byte position within the block defined by the MIRROR_BLOCK byte (beginning of ASCII mirror)                                                                                                                                                                                                                                          |

| FM24NC512T1 | 08A4h        | 29h           | SLEEP_EN         | 1   | 0b             | Enables the SLEEP mode function                                                                                                                                                                                                                                                                                                                            |

| FM24NC512T1 | 08A4h        | 29h           | STRG_MOD_E<br>N  | 1   | 0b             | Controls the tag modulation strength - by default strong modulation is enabled                                                                                                                                                                                                                                                                             |

| FM24NC512T1 | 08A4h        | 29h           | FDP_CONF         | 2   | 11h            | FDP CONF defines the configuration of the Field detect pin 00b enabled by first State-of-Frame (start of communication) 01b enabled by halt with previous read operation 10b enabled by selection of the tag 11b enabled by field presence                                                                                                                 |

| FM24NC512T1 | 08A6h        | 29h           | MIRROR_BLO<br>CK | 8   | 00h            | MIRROR_BLOCK defines the block for the beginning of the ASCII mirroring A value >03h enables the ASCII mirror feature 04h-24h valid MIRROR_BLOCK values for FM24NC512T1 (UID ASCII mirror) 04h-26h valid MIRROR_BLOCK values for FM24NC512T1 (NFC counter mirror only) 04h-22h valid MIRROR_BLOCK values for FM24NC512T1 (both UID and NFC counter mirror) |

| FM24NC512T1 | 08A7h        | 29h           | AUTH0            | 8   | FFh            | AUTHO defines the block address from which the password verification is required. Valid address range for byte AUTHO is from 00h to FFh.                                                                                                                                                                                                                   |

|             | D1 -         | Disala        |                         | ſ   | D-6!           |                                                                                                                                                                                              |

|-------------|--------------|---------------|-------------------------|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part number | Byte address | Block address | Field                   | Bit | Default values | description                                                                                                                                                                                  |

|             |              |               |                         |     |                | If AUTH0 is set to a block address which is higher than the last block from the user configuration, the password protection is effectively disabled.                                         |

| FM24NC512T1 | 08A8h        | 2Ah           | PROT                    | 1   | 0b             | One bit inside the ACCESS byte defining the memory protection  Ob write access is protected by the password verification  1b read and write access is protected by the password verification |

| FM24NC512T1 | 08A8h        | 2Ah           | CFGLCK                  | 1   | 0b             | Write locking bit for the user configuration excluding the PWD and PACK 0b user configuration open to write access 1b user configuration permanently locked against write access             |

| FM24NC512T1 | 08A8h        | 2Ah           | NFC_CNT_EN              | 1   | 0b             | Enables the NFC counter<br>0b disabled<br>1b enabled                                                                                                                                         |

| FM24NC512T1 | 08A8h        | 2Ah           | NFC_CNT_PW<br>D_PROT_EN | 1   | 0b             | enables the password protection to read out and mirror the NFC counter 0b the protection is disabled 1b the protection is enabled                                                            |

| FM24NC512T1 | 08A8h        | 2Ah           | AUTHLIM                 | 3   | 000b           | Limitation of negative password verification attempts 000b limiting of negative password verification attempts disabled 001b-111b maximum number of negative password verification attempts  |

| Part number | Byte | Block address | Field           | Bit | Default values | description                                                                                                                                                                                |

|-------------|------|---------------|-----------------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FM24NC512T2 |      |               | MIRROR_CON<br>F | 2   | 00b            | Defines which ASCII mirror shall be used, if the ASCII mirror is enabled by a valid MIRROR_BLOCK byte 00b no ASCII mirror 01b UID ASCII mirror 10b Counter mirror 11b UID & counter mirror |

|             | Byte  | Block   |                  |     | Default | FM                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------|---------|------------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part number |       | address | Field            | Bit | values  | Aperintian                                                                                                                                                                                                                                                                                                                                                 |

| FM24NC512T2 | 0A0Ch | 83h     | MIRROR_BYT<br>E  | 2   | 00b     | The 2 bits define the byte position within the block defined by the MIRROR_BLOCK byte (beginning of ASCII mirror)                                                                                                                                                                                                                                          |

| FM24NC512T2 | 0A0Ch | 83h     | SLEEP_EN         | 1   | 0b      | Enables the SLEEP mode function                                                                                                                                                                                                                                                                                                                            |

| FM24NC512T2 | 0A0Ch | 83h     | STRG_MOD_E<br>N  | 1   | 0b      | Controls the tag modulation strength - by default strong modulation is enabled                                                                                                                                                                                                                                                                             |

| FM24NC512T2 | 0A0Ch | 83h     | FDP_CONF         | 2   | 11h     | FDP CONF defines the configuration of the Field detect pin 00b enabled by first State-of-Frame (start of communication) 01b enabled by halt with previous read operation 10b enabled by selection of the tag 11b enabled by field presence                                                                                                                 |

| FM24NC512T2 | 0A0Eh | 83h     | MIRROR_BLO<br>CK | 8   | 00h     | MIRROR_BLOCK defines the block for the beginning of the ASCII mirroring A value >03h enables the ASCII mirror feature 04h-7Eh valid MIRROR_BLOCK values for FM24NC512T2 (UID ASCII mirror) 04h-80h valid MIRROR_BLOCK values for FM24NC512T2 (NFC counter mirror only) 04h-7Ch valid MIRROR_BLOCK values for FM24NC512T2 (both UID and NFC counter mirror) |

| FM24NC512T2 | 0A0Fh | 83h     | AUTH0            | 8   | FFh     | AUTHO defines the block address from which the password verification is required. Valid address range for byte AUTHO is from 00h to FFh. If AUTHO is set to a block address which is higher than the last block from the user configuration, the password protection is effectively disabled.                                                              |

| FM24NC512T2 | 0A10h | 84h     | PROT             | 1   | 0b      | One bit inside the ACCESS byte defining the memory                                                                                                                                                                                                                                                                                                         |

|             | F.           | F             | F                       | _   | TE .           | FM                                                                                                                                                                                          |

|-------------|--------------|---------------|-------------------------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part number | Byte address | Block address | Field                   | Bit | Default values | description                                                                                                                                                                                 |

|             |              |               |                         |     |                | protection 0b write access is protected by the password verification 1b read and write access is protected by the password verification                                                     |

| FM24NC512T2 | 0A10h        | 84h           | CFGLCK                  | 1   | 0b             | Write locking bit for the user configuration excluding the PWD and PACK 0b user configuration open to write access 1b user configuration permanently locked against write access            |

| FM24NC512T2 | 0A10h        | 84h           | NFC_CNT_EN              | 1   | 0b             | Enables the NFC counter<br>0b disabled<br>1b enabled                                                                                                                                        |

| FM24NC512T2 | 0A10h        | 84h           | NFC_CNT_PW<br>D_PROT_EN | 1   | Ob             | enables the password protection to read out and mirror the NFC counter 0b the protection is disabled 1b the protection is enabled                                                           |

| FM24NC512T2 | 0A10h        | 84h           | AUTHLIM                 | 3   | 000b           | Limitation of negative password verification attempts 000b limiting of negative password verification attempts disabled 001b-111b maximum number of negative password verification attempts |

| Part number | Byte address | Block address | Field           | Bit | Default values | description                                                                                                                                                                                |

|-------------|--------------|---------------|-----------------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FM24NC512T3 | 0B8Ch        | E3h           | MIRROR_CON<br>F | 2   | 00b            | Defines which ASCII mirror shall be used, if the ASCII mirror is enabled by a valid MIRROR_BLOCK byte 00b no ASCII mirror 01b UID ASCII mirror 10b Counter mirror 11b UID & counter mirror |

| FM24NC512T3 | 0B8Ch        | E3h           | MIRROR_BYT<br>E | 2   | 00b            | The 2 bits define the byte position within the block defined by the MIRROR_BLOCK byte (beginning of ASCII mirror)                                                                          |

| FM24NC512T3 | 0B8Ch        | E3h           | SLEEP_EN        | 1   | 0b             | Enables the SLEEP mode function                                                                                                                                                            |

| FM24NC512T3 | 0B8Ch        | E3h           | STRG_MOD_E      | 1   | 0b             | Controls the tag modulation                                                                                                                                                                |

| Dowt        | Byte  | Block   | F:-1.1           | D:- | Default | de a suite di su                                                                                                                                                                                                                                                                                                                                           |

|-------------|-------|---------|------------------|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part number |       | address | Field            | Bit | values  | description                                                                                                                                                                                                                                                                                                                                                |

|             |       |         | N                |     |         | strength - by default strong modulation is enabled                                                                                                                                                                                                                                                                                                         |

| FM24NC512T3 | 0B8Ch | E3h     | FDP_CONF         | 2   | 11h     | FDP CONF defines the configuration of the Field detect pin 00b e enabled by first State-of-Frame (start of communication) 01b enabled by halt with previous read operation 10b enabled by selection of the tag 11b enabled by field presence                                                                                                               |

| FM24NC512T3 | 0B8Eh | E3h     | MIRROR_BLO<br>CK | 8   | 00h     | MIRROR_BLOCK defines the block for the beginning of the ASCII mirroring A value >03h enables the ASCII mirror feature 04h-DEh valid MIRROR_BLOCK values for FM24NC512T3 (UID ASCII mirror) 04h-E0h valid MIRROR_BLOCK values for FM24NC512T3 (NFC counter mirror only) 04h-DCh valid MIRROR_BLOCK values for FM24NC512T3 (both UID and NFC counter mirror) |

| FM24NC512T3 | 0B8Fh | E3h     | AUTH0            | 8   | FFh     | AUTHO defines the block address from which the password verification is required. Valid address range for byte AUTHO is from 00h to FFh. If AUTHO is set to a block address which is higher than the last block from the user configuration, the password protection is effectively disabled.                                                              |

| FM24NC512T3 | 0B90h | E4h     | PROT             | 1   | 0b      | One bit inside the ACCESS byte defining the memory protection 0b write access is protected by the password verification 1b read and write access is protected by the password verification                                                                                                                                                                 |

| FM24NC512T3 | 0B90h | E4h     | CFGLCK           | 1   | 0b      | Write locking bit for the user                                                                                                                                                                                                                                                                                                                             |

|             | -            | -             | _                       |     |                |                                                                                                                                                                                             |  |

|-------------|--------------|---------------|-------------------------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Part number | Byte address | Block address | Field                   | Bit | Default values | description                                                                                                                                                                                 |  |

|             |              |               |                         |     |                | configuration excluding the PWD and PACK 0b user configuration open to write access 1b user configuration permanently locked against write access                                           |  |

| FM24NC512T3 | 0B90h        | E4h           | NFC_CNT_EN              | 1   | 0b             | Enables the NFC counter<br>0b disabled<br>1b enabled                                                                                                                                        |  |

| FM24NC512T3 | 0B90h        | E4h           | NFC_CNT_PW<br>D_PROT_EN | 1   | 0b             | enables the password protection to read out and mirror the NFC counter 0b the protection is disabled 1b the protection is enabled                                                           |  |

| FM24NC512T3 | 0B90h        | E4h           | AUTHLIM                 | 3   | 000b           | Limitation of negative password verification attempts 000b limiting of negative password verification attempts disabled 001b-111b maximum number of negative password verification attempts |  |

| Part number | Byte address | Block address    | Field           | Bit | Default values | description                                                                                                                                                                                |

|-------------|--------------|------------------|-----------------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FM24NC512T4 | 0F70h        | DCh(Se<br>ctor1) | MIRROR_CON<br>F | 2   | 00b            | Defines which ASCII mirror shall be used, if the ASCII mirror is enabled by a valid MIRROR_BLOCK byte 00b no ASCII mirror 01b UID ASCII mirror 10b Counter mirror 11b UID & counter mirror |

| FM24NC512T4 | 0F70h        | •                | MIRROR_BYT<br>E | 2   | 00b            | The 2 bits define the byte position within the block defined by the MIRROR_BLOCK byte (beginning of ASCII mirror)                                                                          |

| FM24NC512T4 | 0F70h        | DCh(Se ctor1)    | SLEEP_EN        | 1   | 0b             | Enables the SLEEP mode function                                                                                                                                                            |

| FM24NC512T4 | 0F70h        | •                | STRG_MOD_E<br>N | 1   | 0b             | Controls the tag modulation strength - by default strong modulation is enabled                                                                                                             |

| FM24NC512T4 | 0F70h        | DCh(Se ctor1)    | FDP_CONF        | 2   | 11h            | FDP CONF defines the configuration of the Field detect pin 00b e enabled by first State-of-Frame (start of communication)                                                                  |

|             | Byte  | Block            | [                |     | Default | FM                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-------|------------------|------------------|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Part number |       | address          | Field            | Bit | values  | description                                                                                                                                                                                                                                                                                                                                                                    |

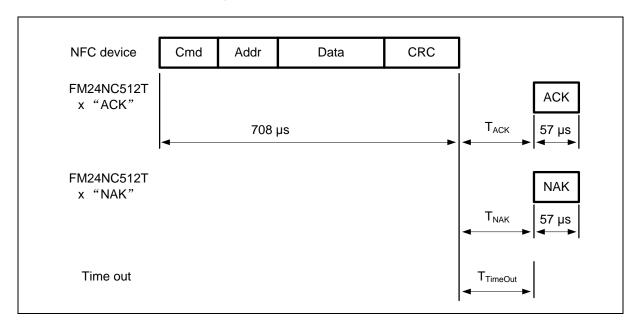

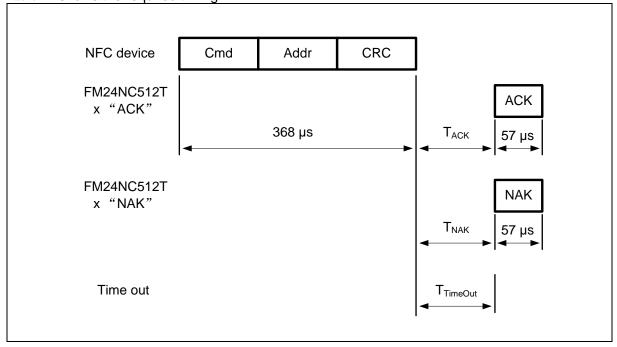

|             |       |                  |                  |     |         | 01b enabled by halt with previous read operation 10b enabled by selection of the tag                                                                                                                                                                                                                                                                                           |